| | 1 | == RMAP Processor == |

| | 2 | |

| | 3 | |

| | 4 | |

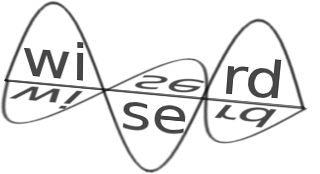

| | 5 | __Figure 1 - RMAP Processor IO__ |

| | 6 | [[BR]][[BR]] |

| | 7 | [[Image(blk_rmap_proc.jpg)]] |

| | 8 | [[BR]][[BR]] |

| | 9 | |

| | 10 | __Table 1 - Tx Command Generator Interface__ |

| | 11 | ||'''Signal Name'''||'''In/Out'''||'''Width'''||'''Description'''|| |

| | 12 | ||''sof''||In||1||Start of frame signal || |

| | 13 | ||''eof'' ||In||1 ||End of frame signal|| |

| | 14 | ||''data''||In||32||input data|| |

| | 15 | ||''wr_en''||In||1||data enable signal|| |

| | 16 | ||''full_flag||Out||1||rmap fifo full flag|| |

| | 17 | [[BR]] |

| | 18 | |

| | 19 | __Table 2 - RMAP Interface__ |

| | 20 | ||'''Signal Name'''||'''In/Out'''||'''Width'''||'''Description'''|| |

| | 21 | ||''addr'' ||Out ||32 ||RMAP address signals || |

| | 22 | ||''data'' ||Out ||32 ||RMAP data signals|| |

| | 23 | ||''cs'' ||Out ||1 ||chip select, active high when RMAP is being accessed|| |

| | 24 | ||''rnw'' ||Out ||1 ||Read/Write, '1' - Read, '0' - Write || |

| | 25 | ||''rd_ack'' ||In ||1 ||Read ack signal, signals end of read cycle e.g. sample read data|| |

| | 26 | ||''wr_ack'' ||In ||1 ||Write ack signal, signals end of write cycle|| |

| | 27 | ||''rd_data'' ||In ||32 ||read data, in sync with rd_ack|| |

| | 28 | ||''intr'' ||In ||1 ||Interrupt, this signal is edge-detected inside RMAP processor|| |

| | 29 | [[BR]] |

| | 30 | |

| | 31 | __Table 3 - Rx Memory Control interface__ |

| | 32 | ||'''Signal Name'''||'''In/Out'''||'''Width'''||'''Description'''|| |

| | 33 | ||''req'' ||Out ||1||request signal, hold until ack|| |

| | 34 | ||''ack'' ||In ||1||ack from Rx memory control, single clock pulse|| |

| | 35 | ||''sof'' ||Out ||1 ||start of frame, || |

| | 36 | ||''eof'' ||Out ||1 ||end of frame|| |

| | 37 | ||''data'' ||Out ||32||data|| |

| | 38 | || || || || 1st word - type field e.g. 0x2000 for generic data, 0x2001 for interrupt (sof == 1)|| |

| | 39 | || || || || 2nd word - rmap address field|| |

| | 40 | || || || || 3rd word - rmap read data field (eof == 1)|| |

| | 41 | ||''data_en'' ||Out ||1 ||data enable, high when data is valid|| |

| | 42 | |

| | 43 | |

| | 44 | [..] |